|

AN/UYS-1先進信號處理器(ASP) AN/UYS-1先進信號處理器(Advanced Signal Processor,ASP)是美國發展的第一種可編程信號處理器,其系統針對高速模組化信號處理應用而優化。早期ASP的研究計畫代號為希臘神話中的普特斯(Proteus),之後美國海軍也常以普特斯來稱呼AN/UYS-1。 AN/UYS -1的發展工作始於1970年代,早期發展由美國海軍航空司令部(NAVAIR)底下的海軍空用發展中心(Naval Air Development Center,NADC)負責,1973年由IBM位於維吉尼亞州馬納薩斯市(Manassas)的分部(1996年由洛克西德.馬丁合併)在競標中獲勝 並取得發展合約;由IBM發展的先進發展模型(Advanced Development Models,ADMs)滿足所有要求的性能指標後,一部份組 件又經過重新設計來增加可靠度、可維修性以及滿足服役週期成本(包含購置、維護等)要求。AN/UYS-1的初期少量生產作業始於1979年,1981年 進入全速率量產。在1985年,AN/UYS-1先進信號處理器的計畫管理責任從NAVAIR轉移給海上系統司令部(NAVSEA),之後又轉移給水下武 器系統專案辦公室(PEO (USW))。使用AN/UYS-1信號處理器的系統包括P-3C陸基長程反潛巡邏機、海軍S-3B艦載反潛機、海軍艦載AN/SQQ-89反潛作戰系 統以及AN/SQR-17A(V)1/2反潛聲納信號處理器(用於改良型諾克斯級)、美國空軍機動地面終端站台(Mobile Ground Terminal ,MGT)等。 隨著1980年代美國國防部推行「第二商源」政策,國防部PMS428辦公室指定一部份AN/UYS-1的組件如高容量模組(High Volume

Modules,HVM)需要在主承包商IBM以外開闢第二商源。在1987年,漢緯(Honeywell)公司在競爭中獲勝,成為AN/UYS-1的

HMV第二供應商,隨後AN/UYS-1的HMV在1988、1989年都維持雙來源供貨。然而,漢緯HMV生產控制程序被發現問題,使美國海軍在

1990年開始研究調查,雖然調查結果顯示主要責任並非在漢緯,然而評估修正這些問題所需的成本, 基本結構

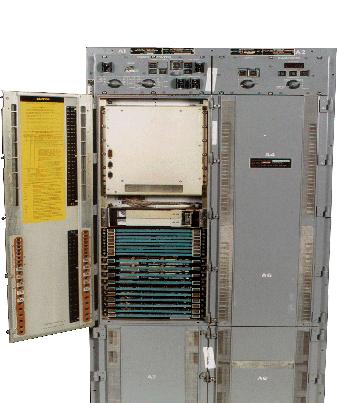

AN/UYS-1的機櫃。 AN/UYS-1由四個子系統組成,每個子系統模組的尺寸大致約為2.2 x 6.9吋,各自擁有自己的背板(backpanel):

AN/UYS-1生產型號有兩種機櫃構型,第一種是氣冷型,機櫃裡裝置單一的AN/UYS-1,依照不同的載台又有多種衍生構型;第二種是潛艦專用的三ASP(TriASP)構型,使用水冷機櫃,結合三部AN/UYS-1。 AN/UYS-1的平均主要失效時間(MTBF)為590小時,平均修復時間(BTTR)為20分鐘。 AN/UYS-1A 新主機板將原本「大容量資料儲存裝置」的儲存控制器功能封裝到主機板上的現場可程式化邏輯閘陣列(Field Programmable Gate Arrays,FPGAs)中,並以新的雙連接埠儲存裝置(Dual Port Bulk Store,DPBS)

取代原本的大容量儲存裝置,使DRAM容量從原本的4M bytes(1M words)提高到8M Bytes(2M

words),並可進一步擴充到16M bytes(4M words);此外,UYS-1A的儲存裝置還增加208

MB的預處理器(Pre-Processor)儲存體。運算處理方面,原本UYS-1的整體運算產出(Throughput)為每秒60萬個定點運算(60

MOPS),使用新的商規組件的UYS-1A則大幅提高到每秒19.2億次浮點運算(1920 M(1.92G) FLOPS)。新主機板還提供了1080 MB的格式化資料儲存體。雖然更新了主機板,AN/UYS-1原本的軟體並不需要更動。 原本AN/UYS -1基本型的背板的I/O通道包括8個供被動聲納浮標使用的定向信號分析記錄(Directional Frequency Analysis and Recording,DIFAR)通道與4個供主/被動聲納浮標使用的先進聲納浮標通信資料鏈(Advanced Sonobuoy Communications Link,ASCL)通道(用於SH-60B LAMPS 3反潛直昇機的UYS-1有五個ASCL通道);而AN/UYS -1A的新主機板則增為32個DIFAR、32個ASCL並加上光纖分散數位介面(FDDI)、PDC、NTDS、1553B資料匯 流排;此外,新主機板還提供了一個四插槽6U VME介面,其他擴充硬體能透過擴充卡(riser board)連接到VME插槽;而主機板上還結合了介面功能,作為AN/UYS-1的控制排線以及VME插槽的介接。此一四插槽VME介面能連接一個嵌入式單板電腦( single board computer)或至多三個數位信號處理器(DSP),能結合在AN/UYS-1的處理器架構下一同運作,增強整個系統的計算處理能力。除了執行原有的應用程式之外,新主機板還能執行由新出現的美國軍規ADA高階語言或商用C語言所撰寫的軟體。

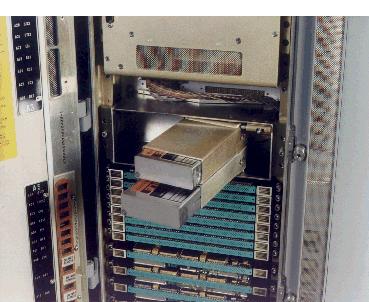

AN/UYS-1A的機櫃,此時安裝了COTS商規插入組件

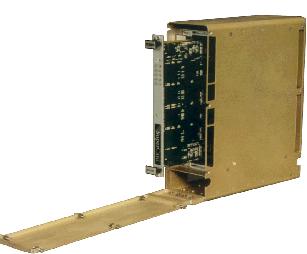

AN/UYS-1A機櫃,圖中的可抽換式硬碟能插入VME擴充槽。

VME擴充槽總成;在1990年代美國改進軍規計算機系統、引進開放式架構時, 加入VME擴充槽是擴充硬體的常見方式。 雖然新的

COTS硬體能力大幅強化,但UYS-1A機櫃的尺寸維持不變(23.27 x 57.31 x

16.02吋),重量大至與原系統持平(原本UYS-1機櫃重250磅,UYS-1A重254磅)。原本UYS-1的電源功率為1800W,而UYS-

1A則略降至1791W。 除了潛艦使用的三ASP版本之外,前述COTS升級方案適用於所有的AN/UYS-1系統;潛艦版由於使用特殊的水冷型主機背板,需要另外編列預算才能進行開發,不過美國海軍潛艦社群並沒有這類計畫。

AN/UYS-2增強模組化信號處理器(EMSP) 在AN/UYS-1在1980年代投入量產之後,美國海軍進一步開發更新一代的AN/UYS-2增強模組化信號處理器(Enhanced Modular Signal Processor,EMSP(Enhanced Modular Signal Processor,EMSP)(Enhanced Modular Signal Processor,EMSPEnhanced Modular Signal Processor,EMSP)),以因應各種新武器系統激增的信號處理需求。 AN/UYS-2是一種採用分散架構、平行處理、資料流(data-flow)結構的信號處理器架構,並採用模組化設計,使之能輕易進行擴充以及容納新的技術插入(technology insertion)。為了支持資料流結構、提供動態的演算法執行排程以及處理器分配工作,AN/UYS-2引進了新開發的處理圖像方法(Processing Graph Method,PGM)。AN/UYS-2採用開放式系統架構,引進現成商規組件(COTS)技術,透過VME擴充槽結合商規硬體,能以最簡易的擴充硬體方式讓既有應用軟體發揮最大功效,並提供適合近岸環境(littoral)的演算法給聲學或未來的非聲學傳感裝置。 依照原始計畫,AN/UYS-2會用於P-3C反潛機的第四階段升級(Update IV,後來被國會取消)、為SH-60反潛直昇機發展的空載低頻聲納系統(Airborne Low Frequency Sonar ,ALFS)、水面艦使用的AN/SQQ-89反潛作戰系統、供戰略音響監視船(SURTASS)使用的AN/UQQ-2低頻拖曳陣列聲納系統、SSN 21海狼(Sea Wolf)核能攻擊潛艦等。 發展歷程 由於考慮到未來的尖端水下聲學演算法,五角大廈PMS428專案管理辦公室以兩階段競標來發展AN/UYS-2:第一階段(Phase 1)是競爭性的概念展示與驗證階段(competitive Demonstration and Validation Phase),在1981年9月啟動;第二階段(Phase 2)則是全規模發展(Full Scale Development,FSD),在1982年8月啟動。第一階段有五家廠商參加,分別是AT&T Technologies、 休斯(Hughes)、控制資料集團(Control Data Corp.)、IBM以及Magnavox,每家廠商都獲得一個固定價格(Fixed-Price) 發展合約,進行概念驗證、關鍵項目展示以及相關的支持分析報告等,授與每一個競爭團隊的合約都包括繼續進行第二階段的選擇權(簽約時價格未定)。第一階段 結束時,美國海軍根據各家廠商的結果,選擇AT&T Technologies(在1995年成為朗訊科技,Lucent Technologies)作為第二階段的主合約商,簽署的合約是固定價格加激勵(Cost Plus Fixed Fee);第二階段的發展工作包括完成三個功能發展模組(Functional Development Models,FDMs)、一個工程原型模型(Engineering Prototype Model,EPM),兩者都是之後AT&T進一步開發所使用 ,此外還要向美軍交付一個實驗室發展裝備(Laboratory Development Equipment,LDE)以及發展測試裝備(Development & Test Equipment,DTE),作為美國海軍進行EMSP與其他武器系統整合的相關工作;此外,還包括為DTE準備用來插入(insertion)的VHSIC技術應用。 在1991年,由於美蘇全面和解,美國國防部進行大規模的國防計畫重新審查,而當時國防部就有意取消AN/UYS-2(V)的發展計畫;當時原本美軍的幾個EMSP原訂終端用戶(如NTDS-B、SCSI I/O、ALFS 、SQQ-89等相關計畫單位)都打算各自開發信號處理器來滿足各自的需求,並認為這樣成本與風險會低於EMSP。然而,美國國會否決了國防部關於取消EMSP的請求,並通過 AN/UYS-2A的多年份採購(Multi-Year Procurement,MYP)授權;同時,美國國會也減少對於這些用戶單位的個別預算,把更多經費集中到國防部PMS428辦公室的EMSP計畫項目之下,以支應這個多年份採購計畫。爾後,PMS 428專案辦公室以聲學系統整合計畫(Acoustic System Integration Program,ASIP)來執行AN/UYS-2A的MYP採購計畫。 基本軟硬體架構 AN/UYS-2的系統架構包含六個核心的功能組件(Functional Elements,FEs),分別是演算法處理器(Arithmetic Processors,AP)、全局記憶體(Global Memories,GMs)、輸入/輸出處理器(Input/Output Processors,IOPs)、通用程式處理器(Command Program Processor,CPP)、排程器(Scheduler,SCH)以及資料傳輸網路(Data Transfer Network,DTN);此外,還可以選擇依照不同的應用,加裝一個名為輸入信號調節器(Input signal Conditione,ISC)的功能組件,作為AN/UYS-2與聲納浮標或其他聲學子系統的介面。這些核心功能組件以及所屬的電源、冷卻系統都根據安裝的平台與應用方式,進行相對應的適當封裝。根據不同系統的需求以及條件,配套的AN/UYS-2選擇不同的功能組件(如AP、GM、IOP、ISC等)組合,達成最適當的配置(包括運算能力、功能、體積重量與功率消耗等);而如果未來運算能力需要成長,AN/UYS-2可直接增加功能組件的數量。AN/UYS-2的通用程式處理器(CPP)、輸入/輸出處理器(IOP)以商規Motorola 68020電腦(32位元定址、多處理器架構)來架構,最大整體I/O傳輸速率為每秒5M bytes,而爆發傳輸速率(rst rate)為40 Mbytes。 AN/UYS-2的相關軟體分成五類(Categories): 1.Category A.1:應用發展(Application Development) 2.Category A.2:機器常駐(Machine Resident) 3.Category B:產品維持(Product Management) 4.Category C: 生產與測試(Manufacturing and Test) 5.Category SEF:軟體工程設施(Software Engineering Facility) 其中,Categories A.1與A.2軟體都是EMSP本身的系統軟體(EMSP System Software,ESS);其餘三種則是用於支援與管理的相關軟體,主要由承包商以及國防部PMS428專案辦公室的電腦計畫支援活動(Computer Program Support Activity)等單位使用。 從SEM B到SEM E 在第二階段發展時,EMSP使用的硬體規格稱為SEM B,用於一般陸基/艦基系統。對於航空系統用戶而言,處理器的體積/重量與功率消耗有著嚴格的限制;為此,EMSP的一個重要的發展,就是把原本的SEM B規格,以更新的電子技術重新封裝,以滿足空基系統用戶的需求,而新的規格稱為SEM E。由SEM B轉換到SEM E時,會保留原本的基本結構、邏輯設計與處理器,但重新封裝到更先進的積體電路技術中,在減低體積重量時提高了性能。SEM E規格大量使用特殊應用積體電路(Application Specific Integrated Circuit,ASIC),其記憶體與邏輯閘陣列的密度都比SEM B的硬體規格更高,單位體積/重量內的運算能力顯著高於SEM B。過去在SEM B之下,每個功能組件(FE)是分立裝置,中間需要接線;而SEM E規格就將每個FE封裝在單一的多層主機板上,免除了中間的接線。在SEM B硬體規格之下,有43種通用的AN/UYS-2 SEM類型;而轉換到SEM E規格時,就大幅減少到10種類型。SEM E規格大幅簡化的硬體結構,使得後勤維護需求比SEM B大幅降低,可靠度顯著提高。 除了指令程式( command programs)以及輸入/輸出程式(I/O program)之外,SEM B與SEM E產品線的軟體是相容的;在指令程式方面,SEM B由較老的CMS-2高階語言撰寫,而SEM B則改用較新的ADA高階語言撰寫,以在SEM E的通用程式處理器(CPP)執行。SEM E重寫的指令程式如果透過原本的SEM B處理圖像(processing graphs)以及機器常駐軟體( machine resident software)來編譯,就可以產出SEM E機器的可執行映像檔(executable program image)。 轉換為SEM E的發展計畫分成兩個階段:第一階段是概念設計(Conceptual Design), 第二階段是全面規模發展(FSD,依照第一階段發展的方式重新封裝整個系統);其中,概念設計階段會產出重置EMSP硬體架構的設計,並評估對程式文件、 可靠度/維護/可獲得性(Reliability, Maintainability, & Availability,RM&A)、後勤計畫造成的影響,這些作業使開發團對能順利地過渡到第二階段;而到了第二階段(FSD)時則產製出三個工程模型,分別是功能發展模型(FDM,用於實驗室測試)、工程原型模型(EPM,用於系統整合測試)以及一個發展測試裝備(DTE,用於可靠度改進測試)。 除了P-3C、SH-60等空載系統的AN/UYS-2使用SEM E硬體規格之外,艦載系統如戰略音響監視船的版本也從SEM B升級到了SEM E;然而,海狼級潛艦的AN/UYS-2似乎沒有進行這樣的升級程序(在日後應該直接使用更新的升級方式)。 AN/UYS-2 COTS組件版 (ACV) 為了讓AN/UYS-2在整個服役週期中維持良好的成本效益,美國海軍在1996年12月啟動AN/UYS-2 COTS衍生型(Variant,ACV)發展計畫,把整個AN/UYS-2A轉換成開放式(Open System Architecture,OSA,需滿足國防部PMA299定義)系統架構,以時下商規現成組件(COTS)全面替換舊硬體。原本AN/UYS-2的主承包商朗訊科技(Lucent Technologies,前T&T/FSAT)依舊是AN/UYS-2 ACV的主承包商。 ACV的主要目的是在過時的舊硬體被新硬體取代時,仍能讓UYS-2既有的軟體在最新的COTS商規硬體上執行,並提供一個彈性且有效的系統架構來因應未來的信號處理發展。為此,ACV透過良好規劃的計算機程式設計方法(Programming Graph Methodology),規劃一系列中介軟體以及應用程式介面(Application Program Interfaces,API);原本UYS-2的PGM應用軟體透過這些中介層,得以在COTS商規硬體上運行的作業系統環境中執行,兩者完全隔絕。這些API讓UYS-2原有的應用軟體在不同的硬體架構下執行,包括工作站或數位信號處理器(DSP)。 在1996年12月,美國海軍進行AN/UYS-2 ACV計畫的初始基線審查(Internal Baseline Review,IBR),在1997年1月進行軟體需求審查(Software Requirements Review,SRR),在1997年5月進行高階設計審查(High Level Design Review),在1997年11月進行細部設計審查(Detailed Design Review),1999年1月進行接收測試預備審查(Acceptance Test Readiness Review),在1999年春季進行系統測試(配合ALFS空載低頻聲納系統的需求)。

在ALFS空載低頻聲納計畫的特殊應用信號處理快速展示原型(Rapid prototyping of Application Specific Signal Processor,RASSP),是結合AN/UYS-2 ACV信號處理器以及新的淺水作業需求而成。ALFS引進運算能力達10億FLOPS的商用浮點運算處理器(Floating Point Commercial Arithmetic Processor,FPCAP),會佔用AN/UYS-2系統的三個插槽,能同時執行回波追蹤識別(Echo Tracker Classifier,ETC) 以及機載合成孔徑雷達(Synthetic Aperture Radar,SAR)的演算法。此種FPCAP的開發計畫在1995年8月展開,設計、發展工作由國防部 PMS428、PMA299專案辦公室以及國防部先進計畫研究局(DARPA)資助,由PMS428領導整個專案,PMS411主要負責研究ETC演算法,而洛克希德.馬丁公司(Lockheed Martin)則負責軟體實作。FPCAP的設計審查在1995年11月以及1996年6月進行,原型在1996年11月完成,第一套在1997年4月交付休斯飛機公司(Hughes Aircraft Company(HAC)來整合於SH-60R直昇機上,整個FPCAP發展計畫在1997年6月完成。 原本AN/UYS-2A的多年份採購計畫中,包括供應108套信號處理器給ALFS空載低頻聲納項目,不過ALFS計畫的需求是188套,然而美國國防部並沒有經費增購另外80套AN/UYS-2A;為此,ACV計畫就包含填補這額外80套處理器的缺口。 以AN/SQQ-89為例,引進AN/UYS-2 ACV的是AN/SQQ-89(V)10,其信號處理升級發展(Signal Processing Upgrade

Development,SPUD)計畫的應用軟體能在AN/SQQ-89(V)Y的通用信號處理器架構(common

signal processing architecture)執行,

而此一通用信號處理器架構由Mercury的數位信號處理器(DSP)模組(由四合一SHARC構成)以及基於PowerPC處理器的模組構成。 |